- TRANSDUCERS

- TRANSDUCERS

- BASIC COMPONENTS DK

- BASIC COMPONENTS DK

- MARKETPLACE

- MARKETPLACE

- DEVELOPMENT BOARDS & KITS

- DEVELOPMENT BOARDS & KITS

- CABLE ASSEMBLIES

- CABLE ASSEMBLIES

- RF AND WIRELESS

- RF AND WIRELESS

- BOXES ENCLOSURES RACKS

- BOXES ENCLOSURES RACKS

- AUDIO PRODUCTS

- AUDIO PRODUCTS

- FANS-BLOWERS-THERMAL MANAGEMENT

- FANS-BLOWERS-THERMAL MANAGEMENT

- WIRELESS MODULES

- WIRELESS MODULES

- TERMINALS

- TERMINALS

- Cables/Wires

- Cables/Wires

- SINGLE BOARD COMPUTER

- SINGLE BOARD COMPUTER

- BREAKOUT BOARDS

- BREAKOUT BOARDS

- LED

- LED

- TEST AND MEASUREMENT

- TEST AND MEASUREMENT

- POTENTIONMETERS AND VARIABLE RESISTORS

- POTENTIONMETERS AND VARIABLE RESISTORS

- DEVELOPMENT BOARDS AND IC's

- DEVELOPMENT BOARDS AND IC's

- EMBEDDED COMPUTERS

- EMBEDDED COMPUTERS

- OPTOELECTRONICS

- OPTOELECTRONICS

- INDUSTRAL AUTOMATION AND CONTROL

- INDUSTRAL AUTOMATION AND CONTROL

- COMPUTER EQUIPMENT

- COMPUTER EQUIPMENT

- CONNECTORS & INTERCONNECTS

- CONNECTORS & INTERCONNECTS

- MAKER/DIY EDUCATIONAL

- MAKER/DIY EDUCATIONAL

- TOOLS

- TOOLS

- MOTORS/ACTUATORS/SOLEENOIDS/DRIVERS

- MOTORS/ACTUATORS/SOLEENOIDS/DRIVERS

- FPGA HARDWARE

- FPGA HARDWARE

- ROBOTICS & AUTOMATION

- ROBOTICS & AUTOMATION

- Home

- SDR

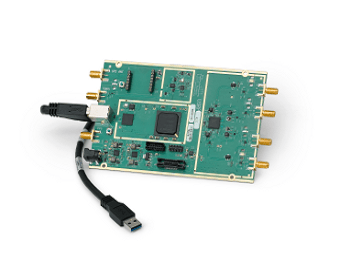

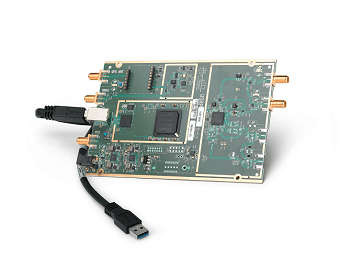

- USRP HARDWARE

- USRP BUS SERIES

USRP BUS SERIES

- 4 itemsThe USRP product family includes a variety of models that use a similar architecture. A motherboard provides the following subsystems: clock generation and synchronization,

The USRP product family includes a variety of models that use a similar architecture. A motherboard provides the following subsystems: clock generation and synchronization, FPGA, ADCs, DACs, host processor interface, and power regulation. These are the basic components that are required for baseband processing of signals. A modular front-end, called a daughterboard, is used for analog operations such as up/down-conversion, filtering, and other signal conditioning. This modularity permits the USRP to serve applications that operate between DC and 6 GHz.

In stock configuration the FPGA performs several DSP operations, which ultimately provide translation from real signals in the analog domain to lower-rate, complex, baseband signals in the digital domain. In most use-cases, these complex samples are transferred to/from applications running on a host processor, which perform DSP operations. The code for the FPGA is open-source and can be modified to allow high-speed, low-latency operations to occur in the FPGA.

Filter

NEWSLETTER

Subscribe to get Email Updates!

Thanks for subscribe.

Your response has been recorded.

INFORMATION

ACCOUNT

ADDRESS

Tenet Technetronics# 2514/U, 7th 'A' Main Road, Opp. to BBMP Swimming Pool, Hampinagar, Vijayanagar 2nd Stage.

Bangalore

Karnataka - 560104

IN

Tenet Technetronics focuses on “Simplifying Technology for Life” and has been striving to deliver the same from the day of its inception since 2007. Founded by young set of graduates with guidance from ardent professionals and academicians the company focuses on delivering high quality products to its customers at the right cost considering the support and lifelong engagement with customers. “We don’t believe in a sell and forget model “and concentrate and building relationships with customers that accelerates, enhances as well as provides excellence in their next exciting project.